## Thèse

présentée pour obtenir le grade de docteur de l'École Nationale Supérieure des Télécommunications

Spécialité : Informatique et Réseaux

## Arnaud Bailly

Du requis au garanti : contrats dans un calcul d'objets temporisés mobiles.

Soutenue le 17 Décembre 2002 devant le jury composé de

Gérard Florin Président

Jean-Pierre Courtiat Rapporteurs

Alessandro Fantechi

Isabelle Demeure Examinateurs

Kathleen Milsted

Jean-Bernard Stefani

Elie Najm Directeur de Thèse

## Remerciements

Je tiens tout d'abord à remercier Elie Najm, qui a été mon directeur de thèse, et qui m'as toujours prodigué son soutien de manière inconditionnelle dans les moments les plus difficiles, et offert son amitié (et un verre de bière en bien des occasions). Pour tout cela je resterai éternellement redevable et reconnaissant envers lui.

Je remercie également Jean-Bernard Stefani et Kathleen Milsted pour avoir accepté de participer au jury de ma soutenance, et pour avoir, en tant que responsables succesifs de l'encadrement de mes travaux pour la section DTL/ASR à France Télécom R&D, permis le financement de la majeure partie de cette thèse.

Je remercie Alessandro Fantechi pour avoir accepté de rapporter cette thèse, et pour les nombreuses discussions que nous avons pu avoir lors de ses visites en France et de nos rencontres de part le monde.

Je remercie aussi chaleureusement Jean-Pierre Courtiat pour avoir rapporté mes travaux, pour sont humour et sa précision dans les commentaires qu'il a pu me prodiguer.

Je remercie bien sûr les professeurs, doctorants, et personnels du département informatique et réseaux de l'ENST, qui ont participé à créer une ambience de travail agréable et stimulante durant ces longues années. Parmis les nombreux doctorants que j'ai pu croiser, et sans volonté d'hexaustivité ni ordre particulier, je tiens à citer les docteurs Wessam Ajib, Didier Verna, Nadine Richard, Abbas Ibrahim, Arnaud Fontaine, Philippe Martins, Muhammad Kazmi, Dany Zebiane, Rani Makke, Pascal Moyal, Alexandre Tauveron, Cyril Carrez, Jean-Pilippe Démoulin, et Robert Bestak. À eux s'ajoutent les plus amicaux participants des «Zappy» du Vendredi et d'autres événements, nommément Abdelkrim Nimour, Arnaud Février, Gaël Chardon, Odile Derouet, Jean Leneutre, Sonia Heimann et Vania Conan, qui ont souvent supporté mes désidérata neuronaux et mes jugements à l'emporte-pièce. Je les en remercie tous bien chaleureusement.

Je remercie tout particulièrement certaines personnes que j'ai eu la chance de croiser, avant ou pendant ma thèse, et qui me maintiennent encore, et ce de manière complètement déraisonnée et incompréhensible, leur soutient démesuré et leur amitié bienveillante. Comme j'ai beaucoup de chance elles sont nombreuses, et leur mérite n'a pas d'égal; aussi elles ne sauraient être comparés entre elles. Je remercie donc Tatiana Aubonnet, Loutfi Nuaymi, Cyril Lacaud, Sophie Diallo, Frédéric Fourneau, Richard Sanders et Jorunn Dugstad. Que nos chemins ne se séparent pas.

Enfin, je remercie mes parents, sans qui tout cela n'aurait pu arriver...

## Résumé

#### Introduction

Les systèmes répartis exhibant des contraintes temporelles sont aujourd'hui présents partout: de bons exemples sont les systèmes de télécommunications numérique ou bien les systèmes embarqués comme rencontrés dans l'électronique grand public ou l'avionique. La conception et le déploiement de tels systèmes sont intrinsèquement complexes. De nombreuses méthodes de développement fondées sur l'analyse formelle de ces systèmes ont donc été proposées. Ces méthodes sont basées sur la description des comportements possibles du système analysé.

Nous soutenons toutefois que les méthodes existantes sont souvent inadaptées car elle ne permettent pas de distinguer les actions que le système *peut* produire des actions qu'il *doit* produire. L'absence de ce pouvoir de distinction conduit à des spécifications purement factuelles, où raisonner à propos d'un système ne peut être accompli que si l'on connaît absolument son environnement, ce dernier pouvant produire des actions interférant avec celles du système étudié.

Nous proposons donc des méthodes de description et d'analyse fondées sur la reconnaissance de cette distinction. La description d'un système indique alors les exigences (ou suppositions, ou assumptions) faite pas le système sur son environnement, ainsi que les garanties respectées par le système quand son environnement se comporte de manière adaptée. L'ensemble forme un contrat entre le système et son environnement.

Nous utilisons pour langage une extension temporisée du  $\pi$ -calcul pour objets mobiles. Nous proposons une notion d'équivalence pour les termes de ce langage fondée sur la bisimulation, ainsi qu'un système de preuve permettant de décider de manière exacte et complète si deux termes à états finis se comportent de manière identique. Cependant, les descriptions utilisant le  $\pi$ -calcul produisent en général un nombre infini d'états.

Nous proposons donc une autre méthode d'analyse, fondée sur le typage comportemental, qui permet de prendre en compte de telles descriptions. Notre système de type nous permet de raisonner de manière compositionelle: chaque élément forme alors un composant, et les composants ne peuvent être assemblés que si chacun d'entre eux ne fait pas de suppositions excessives sur le comportement des autres composants. Vérifier qu'un module se comporte de manière correcte envers son environnement se réduit à vérifier qu'il est bien typé. L'analyse de types étant statique (à la compilation et non à l'exécution) cela permet de savoir si un module est correct dès sa conception.

Enfin nous remarquons que les applications temps-réel dépendent très fortement de leur environnement d'exécution, et la vérification statique ne sert à rien si la machine d'exécution d'un programme (système d'exploitation, machine virtuelle) peut se retrouver dans l'incapacité d'allouer les ressources demandée dynamiquement. Pour cela, il nous parait intéressant d'utiliser les résultats obtenus par typage pour garantir l'exécution correcte des applications. Une machine d'exécution peut en effet utiliser les informations contenues dans les types comportementaux pour prévoir les besoins en ressources système (deadlines, bande passante) et pratiquer un contrôle d'admission à l'entrée. Nous remarquons qu'une preuve de bon typage étant une preuve de bon comportement, elle peut également servir à contrôler le code lui-même, en tant que «proof-carrying code», comme pratiqué actuellement par la machine virtuelle Java. Une application évidente de nos travaux est alors la prévention des «Denial of Service attacks». Nous montrons pour conclure que les notations et méthodes définies sont utilisables dans le cadre de développements utilisant la notation UML-RT.

## Le langage $\pi^{\delta}$

Nous définissons un calcul de processus temporisés permettant de représenter les contraintes exhibées par des composants temps-réel dont le code peut migrer dynamiquement sur un réseaux d'ordinateurs. Chaque processus comprend un terme algébrique t et un contexte  $\rho$  donnant une valeur à des horloges dont la valeur évolue au cours du temps; l'ensemble forme un terme de  $\pi^{\delta}$ , noté tout simplement  $t\rho$ .Les termes t respectent la syntaxe suivante, en prenant a,b,c appartenant à un ensemble infini de noms de ports, et x,y,z appartenant à un ensemble infini de noms d'horloges:

$$t ::= 0 \mid Error^{\upsilon} \mid [\sigma, \, \upsilon]\pi.\, t \mid [a = b]t \mid \nu n \, t \mid t + t \mid t \mid t \mid A(\tilde{n}) .$$

où n peut être indifféremment un nom de port ou d'horloge. Les processus de terme 0 sont appelés processus passifs; les processus de terme Error sont appelés processus bloquants (nous dirons aussi informellement qu'ils sont indésirables, ou qu'ils produisent une erreur). Les opérateurs qui apparaissent dans la syntaxe ci-dessus sont usuellement nommés, de gauche a droite: préfixe, comparaison, restriction, somme (ou choix), composition (ou parallèle), et instanciation.

La syntaxe des actions réductibles est donnée ci-dessous:

$$\pi^* ::= a(n) \mid \overline{a} n \text{ et } \pi ::= \tau \mid \pi^*.$$

L'action silencieuse  $\tau$  peut-être vue comme une action *interne* au processus qui l'effectue. Tous les autres préfixes ont un *sujet a* appartenant à  $\mathbf{P}$ , et un *objet n* appartenant à  $\mathbf{N}$ . Informellement,  $\overline{a}n$  décrit une *émission* sur le port sujet a d'un message contenant l'objet n, et a(n) décrit la réception d'un message sur le port a, dont l'objet reçu est appelé n dans la continuation t du processus.

Les contraintes de sélection  $\sigma$  et les conditions d'urgence v (ou deadlines) respectent la syntaxe suivante, donnée respectivement par

$$\sigma ::= \sigma \wedge \sigma \mid x \sharp^{\sigma} q \mid x - y \sharp q \text{ et } v ::= v \wedge v \mid x \sharp^{v} q \mid x - y \sharp q$$

où  $\sharp \in \{<, \leq, \geq, >\}$ ,  $\sharp^{\sigma} \in \{<, \leq, \geq\}$ ,  $\sharp^{v} \in \{<, \geq\}$ , et q est une valeur décrivant un instant précis dans la marche temporelle. Le processus  $Error^{\top}$ , où  $v = \top$  est la condition toujours vraie, est Error par simplicité.

Le point essentiel est que la sémantique de ces processus décrit ce que chacun d'entre eux offre et exige. Ainsi, un processus présentant un préfixe dont la contrainte  $\sigma$  est vérifiée sans que v soit vérifiée fait une offre à sont environnement. L'environnement est alors libre d'accepter l'offre et de se synchroniser avec le processus offrant, ou bien de refuser. Dans ce dernier cas, le temps peut s'écouler librement. sans qu'aucune action ne se passe. Si toutefois l'action est urgente (dont v) est vraie, alors l'environnement ne peut refuser la synchronisation. S'il ne propose a temps une offre correspondant à l'exigence présentée par le processus, alors ce dernier entraîne tout le système vers une erreur. Les règles de sémantique opérationnelle pour  $\pi^{\delta}$  sont données en Tables 3.2 et 3.3.

#### L'axiomatisation et le système de types

Présenter ici les détails techniques liés à l'axiomatisation ou aux système de types serait déplacé, car leur complexité est trop importante. En place de cela, nous en décrivons les principes. Ces deux contributions techniques reposent sur une sémantique symbolique du langage  $\pi^{\delta}$ .

#### La sémantique symbolique

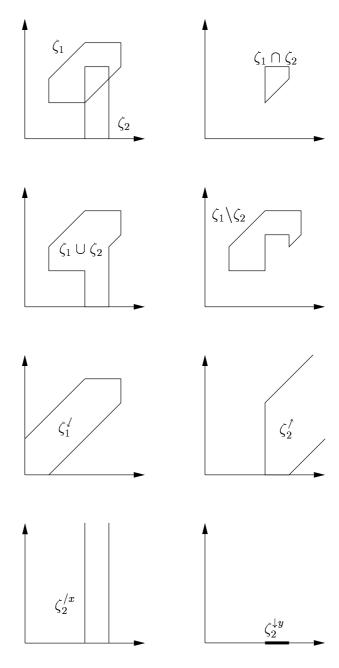

Un problème essentiel posé par l'étude des systèmes temps réels est la nature continue du temps. En effet, un temps continue implique que laisser passer le temps peut aboutir à une infinité de processus différant par la valeur de leurs horloges. Rajeev Alur et David Dill ont montré cependant que, lorsque les valeurs temporelles apparaissant dans les contraintes des termes sont rationnelles, alors qu'une infinité de transitions laissant passer le temps pour un processus peuvent en fait être représentées par une seule transition [AD94]. Une telle transition est dite symbolique, ou abstraite. Les processus reliés par des transitions symboliques sont appelés régions, ou zones (une zone contient plusieurs régions). Un parle aussi de graphe des régions.

L'abstraction proposée par les régions rend de nombreux problèmes décidables pour les processus temporisés dont l'abstraction est à états finis (i.e. la seule source «d'infinitude» provient du temps, le contrôle de ces automates restant à états finis). Cependant, nos processus incluant des termes au moins aussi expressifs que le  $\pi$ -calcul, leur partie de contrôle peut atteindre un nombre infini d'états (le pi-calcul permet d'encoder le  $\lambda$ -calcul [SW01]). C'est la génération de noms (i.e. l'introduction de restrictions) en nombre toujours croissant qui permet à des termes d'atteindre l'infinité en espace. Nous utilisons donc une deuxième forme d'abstraction, celle ci définie par Hennessy et Lin [HL95] permettant d'abstraire la géneration de noms et de la réduire à un fragment finitaire. Cette abstraction permet toujours au processus de générer un espace d'états infini, mais elle permet d'effectuer la comparaison entre processus non sur la base des noms qu'ils génèrent (ce qui est infaisable pratiquement), mais sur la base des comparaisons qu'ils font entre ces noms (ce qui est fait dans le système de preuves).

#### Le système de preuves

Nous avons donc adapté des systèmes de preuve existant [LY02, Lin98], pour permettre de prouver de manière cohérente, valide et complète, que deux processus sont liés par une relation d'équivalence appelée bisimilarité temporisée tardive, qui est une simple extension de la notion de bisimilarité introduite par Milner pour CCS et le  $\pi$ -calcul.

Notre adaptation est cependant non trivialle car une propriété temporelle usuellement respectée ne l'est pas par nos processus, de part leur nature contractuelle représentant des offres et des exigences. En quelques mots, nous devons découper l'espace d'états de nos processus de manière suffisemment fine, ce qui requiert de surcroit d'effectuer des correspondances assez élaborées entre partitions. La complétude du système de preuves est obtenue en permettant d'interrompre la comparaison de différentes branches d'un choix lorsque l'une des branches génère une erreur (et donc interdit d'effectuer toute transition). Ainsi, des processus qui se comporte de manière équivalente avant le bloquage mais auraient pu se comporter de manière différente après sont quand-même identifiés (comme il se doit). Le système de preuves, ainsi que la sémantique symbolique des processus, est décrite au Chapitre 4.

#### Le système de types

Alors que les preuves d'équivalence ne sont faisables que sur des processus à états finis (nous n'autorisons pas l'usgae de la récursion), le système de types permet d'analyser des configurations atteignant un nombre d'états infini. Ceci peut être accompli en effectuant une abstraction supplémentaire sur les noms de ports qui sont créés ou transmis. La sémantique symbolique étant sur ce point plus précise que nos types, nous pouvons l'utiliser pour mener à bien l'analyse des types, résolvant de ce fait les problèmes liés à la nature continue du temps de la même manière que précédemment. Une contrainte forte (mais réaliste) est cependant introduite sur la duplication des noms de ports dans une configuration bien typée: si la forme (i.e. le type) des communications sur un port donné peut évoluer au cours du temps, alors il ne devra pas y avoir plus de deux exemplaires de ce nom dans lénsemble du systèmes: les interactions se font par paires, uniquement par des processus qui sont de cette manière «en vis-à-vis».

Les résultats obtenus sont l'absence de bloquage dû à un manque de synchronisation entre processus (le contrat exhibé par un processus n'est jamais rompu), et l'absence de bloquage de la progression du temps (i.e. le système continue à évoluer, évitant le paradoxe d'Achille et de la tortue décrit par Zénon d'Élée), sous une condition d'équité faible concernant le transitions silencieuses (appelées aussi transitions internes).

#### Les Applications

Nous commençons le chapitre des applications par un peu de litérature comparée autour de la notion de contrat (en logique, essentiellement) et de son utilisation en informatique. Nous établissons un lien en particulier entre la logique déontique telle

que décrite par Von Wright [von51] et nos systèmes à transitions étiquetées portant les offres et les exigences d'un processus.

Ensuite, nous avançons une utilisation possible de  $\pi^{\delta}$  comme langage de modèle pour des plateformes d'exécution temps-réel distribuées. Certaines propositions récentes [MNCK99] vont en effet dans le sens de distinguer des objets "parfaits" ou objets de modèle, qui représentent l'exécution ideale, telle qu'elle devrait se produire, des objects actifs, qui effectuent réellement les tâches calculatoires à accomplir. Les ojets de modèle donnent la structure, la référence de l'application à exécuter. Alors, des ojets de modèles exprimés en  $\mathcal{A}$ rtOC fourniraient un support sémantique précis à la plateforme et au programmeur devant concevoir l'application. À l'exécution, une incompatibilité entre le modèle de l'application et les activités observées de cette application pourraient amener à prendre des mesures contre celle-ci. Cette proposition se rapproche du model-carrying-code [SRRS01].

Enfin, nous présentons un langage d'acteurs appelé  $\mathcal{A}$ rtOC, que nous avons également développé, et dont les principes sont similaires à  $\pi^{\delta}$ . Ce langage est toutefois plus proche des langages de programmation classique, et les communications entre agents se font par passage de message asynchrone, alors que les communications sont synchrones dans  $\pi^{\delta}$ . Cette dernière hypothèse est plus conforme à la réalité, ce qui rapproche le langage de la pratique usuelle, et devrait réduire le temps d'apprentissage moyen pour en arriver à la maîtrise par rapport à  $\pi^{\delta}$ . Nous montrons finalement comment des concepts usités (syntaxiquement) dans des programmes  $\mathcal{A}$ rtOC trouvent un pendant naturel dane le langage de specification UML-RT. Ceci nous mêne a proposer une intégration de programmes  $\mathcal{A}$ rtOC dans un processus de développement de systèmes temps-réel utilisant la notation UML-RT.

#### Conclusion

Nous avons étudié la notion de *contrat* entre objets répartis et temps réel. Cette étude nous apermis de définir formellement un cadre sémantique permettant notemment de comparer notre approche avec de nombreux travaux existants, où la notion de contrat, si elle n'est pas toujours explicite, se trouve mise au jour par notre comparaison. Nous avons également tenté de donner une portée pratique à nos travaux. Si les aspects techniques abordés ont été très satisfaisants de part leur complexité, il est toutefois clair que cette complexité se retrouve au niveau des modèles manipulés. Un défi pour l'avenir serait donc de simplifier certains côtés de l'approche pour en tirer le meilleur, et fournir au programmeur potentiel des outils plus facilement manipulables que ceux qui pourraient être obtenus avec la théorie actuelle. C'est certainement sur ces points pratiques que les contributions de nos travaux sont les plus faibles, et y remédier pourrait s'avérer un chemin d'étude de longueur au moins égale à celle du chemin déjà parcouru.

## Contents

| 1 | Introduction |                                                             |    |

|---|--------------|-------------------------------------------------------------|----|

| 2 | Ope          | en Distributed Processing and Real-Time                     | 19 |

|   | 2.1          | Open Distributed Processing                                 | 19 |

|   |              | 2.1.1 Overview                                              | 19 |

|   |              | 2.1.2 The Computational Viewpoint                           | 20 |

|   |              | 2.1.3 The Engineering Viewpoint                             | 22 |

|   |              | 2.1.4 Specifications, Viewpoints and their Relations        | 23 |

|   | 2.2          | Modeling and Verifying Real-time Systems                    | 23 |

| 3 | An           | Untyped $\pi^{\delta}$ : Syntax and Semantics               | 25 |

|   | 3.1          | Introduction                                                | 25 |

|   | 3.2          | The Syntax: Processes, Ports, and Clocks                    | 27 |

|   | 3.3          | The Time Domain and Its Properties                          | 29 |

|   | 3.4          | Clock Valuations, Constraints, And Satisfaction             | 30 |

|   | 3.5          | Well-Formedness Criteria for Processes                      | 31 |

|   | 3.6          | The Semantics: Labeled Transition Systems for Processes     | 32 |

|   | 3.7          | Semantics of A Small Example                                | 37 |

|   | 3.8          | Model Properties Over Time                                  | 40 |

|   | 3.9          | Discussion and Related Works                                | 41 |

| 4 | A F          | $\textbf{Proof System for}\pi^{\delta}$                     | 45 |

|   | 4.1          | Process Equivalence and Abstract Semantics                  | 45 |

|   |              | 4.1.1 Axiomatizing Dense Time                               | 47 |

|   |              | 4.1.2 Axiomatizing Name Instantiation                       | 48 |

|   |              | 4.1.3 Manipulating Zones, Regions, and Matching Constraints | 49 |

|   |              | 4.1.4 Abstract Labeled Transition Systems                   | 54 |

|   |              | 4.1.5 Semantics of a Small Example (Continued)              | 61 |

|   | 4.2          | Algebraic Laws for Processes                                | 63 |

|   |              | 4.2.1 Relating Concrete and Abstract Transition Systems     | 63 |

|   |              | 4.2.2 Symbolic Timed Late Bisimulation                      | 64 |

|   |              | 4.2.3 A Proof System for Terms with Finite Control          | 66 |

|   |              | 4.2.4 Soundness and Completeness                            | 73 |

|   | 4.3          | Conclusion                                                  | 73 |

12 CONTENTS

| <b>5</b>     | $\mathbf{A}$ | 3ehavi                                  | ${f oral}  {f Type}  {f System}  {f for}  \pi^{\delta}$                 | 77  |  |  |  |

|--------------|--------------|-----------------------------------------|-------------------------------------------------------------------------|-----|--|--|--|

|              | 5.1          | Introd                                  | ${f luction}$                                                           | 77  |  |  |  |

|              | 5.2          | The T                                   | Type Language                                                           | 78  |  |  |  |

|              |              | 5.2.1                                   | The Syntax for Types                                                    | 79  |  |  |  |

|              |              | 5.2.2                                   | Type Semantics                                                          | 80  |  |  |  |

|              |              | 5.2.3                                   | Discourse on The Meaning of Types                                       | 83  |  |  |  |

|              | 5.3          | ~ · · · · · · · · · · · · · · · · · · · |                                                                         |     |  |  |  |

|              | 5.4          | Type                                    | Checking                                                                | 89  |  |  |  |

|              |              | 5.4.1                                   | Restraining the Expressive Power of Processes                           | 89  |  |  |  |

|              |              | 5.4.2                                   | Type Compatibility and Context Composition                              | 91  |  |  |  |

|              |              | 5.4.3                                   | The Type System                                                         | 94  |  |  |  |

|              | 5.5          | Prope                                   | rties of our Type System                                                | 97  |  |  |  |

|              | 5.6          | Livene                                  | ess and Composition                                                     | 99  |  |  |  |

|              | 5.7          | Relate                                  | ed Works and Conclusion                                                 | 101 |  |  |  |

|              |              | 5.7.1                                   | Behavioral Types                                                        | 101 |  |  |  |

|              |              | 5.7.2                                   | Assume/Guarantee Reasoning                                              |     |  |  |  |

|              |              | 5.7.3                                   | Conclusion                                                              | 103 |  |  |  |

| 6            | Applications |                                         |                                                                         |     |  |  |  |

|              | 6.1          | Introd                                  | $\operatorname{luction}$                                                | 105 |  |  |  |

|              | 6.2          | Contr                                   | acts in Logic and Computation                                           | 105 |  |  |  |

|              |              | 6.2.1                                   | Contracts in Deontic Logic                                              |     |  |  |  |

|              |              | 6.2.2                                   | Contracts in Behavioral Types                                           | 106 |  |  |  |

|              |              | 6.2.3                                   | Contracts in Hoare Logic and Its Extensions                             |     |  |  |  |

|              |              | 6.2.4                                   | Contracts in $\pi^{\delta}$                                             | 108 |  |  |  |

|              |              | 6.2.5                                   | Contracts Elsewhere in Computing                                        | 109 |  |  |  |

|              | 6.3          | Prova                                   | ble QoS Support for Middleware Platforms                                | 110 |  |  |  |

|              |              | 6.3.1                                   | QoS Specification                                                       | 111 |  |  |  |

|              |              | 6.3.2                                   | Model Components and Type Checking                                      | 112 |  |  |  |

|              | 6.4          | Integr                                  | ation with UML-RT                                                       | 113 |  |  |  |

|              |              | 6.4.1                                   | $\mathcal{A}\mathbf{rtOC}$ : An actor-like, asynchronous $\pi^{\delta}$ | 113 |  |  |  |

|              |              | 6.4.2                                   | A Meta-Architecture For UML-RT                                          | 116 |  |  |  |

|              |              | 6.4.3                                   | Notions of $\mathcal{A}\mathbf{rtOC}$ in UML                            | 117 |  |  |  |

|              |              | 6.4.4                                   | Relationships with UML-RT and Examples                                  | 121 |  |  |  |

|              | 6.5          | Concl                                   | usion                                                                   | 125 |  |  |  |

| 7            | Cor          | iclusio                                 | n                                                                       | 127 |  |  |  |

| $\mathbf{A}$ | Pro          | ofs                                     |                                                                         | 129 |  |  |  |

## List of Figures

| 2.1  | Communicating roles of an Operational Service $u 	cdots 	$ |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | An example of communicating interfaces, step (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3  | An example of communicating interfaces, step (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4  | An ODP Configuration at Engineering Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1  | Operations on 2-Polyhedra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.1  | The Syntax of $\mathcal{A}rtOC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.2  | The Relationships Among UML-RT Entities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

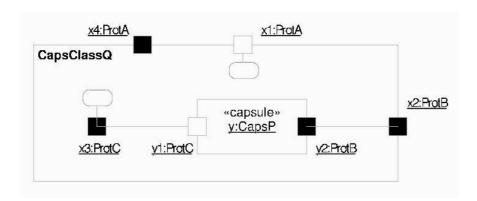

| 6.3  | An UML-RT Collaboration Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

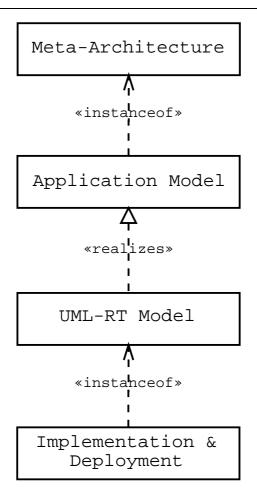

| 6.4  | The "Stack of Models"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

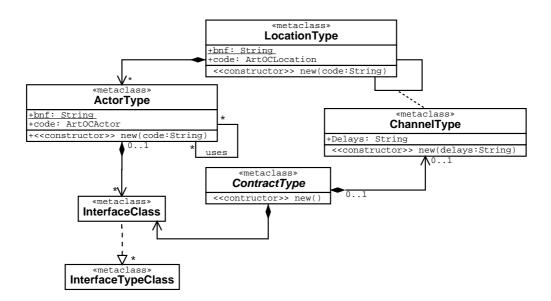

| 6.5  | The Relationships among $\mathcal{A}rtOC$ Meta-Architectural Concepts 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

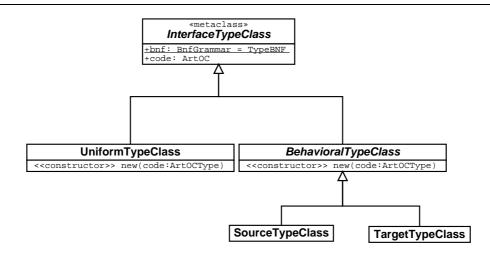

| 6.6  | The Interface Type Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

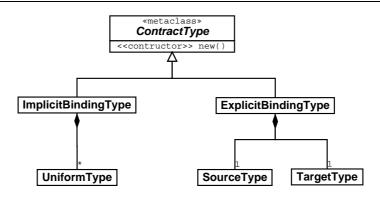

| 6.7  | The Contract Type Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

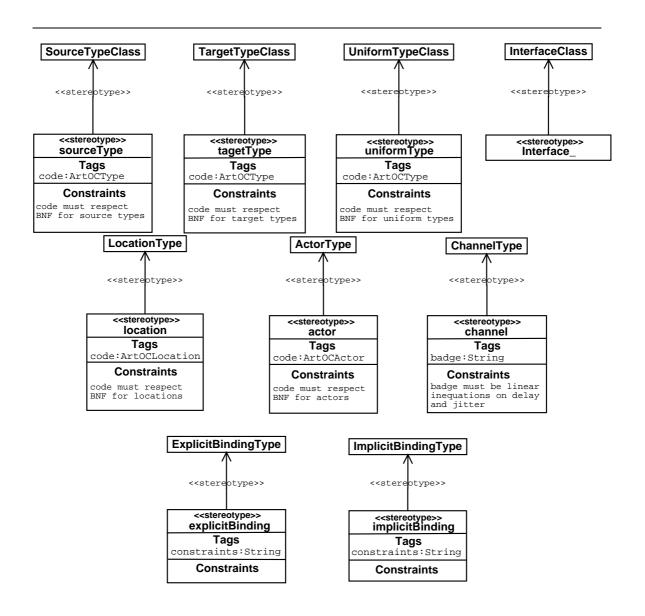

| 6.8  | Stereotypes for $\mathcal{A}rtOC$ Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

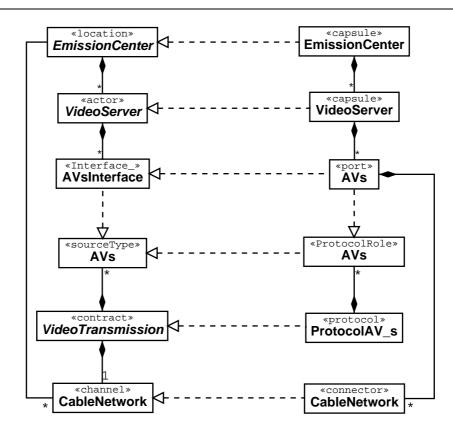

| 6.9  | Realization of UML-RT specifications by $\mathcal{A}rtOC$ Programs 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

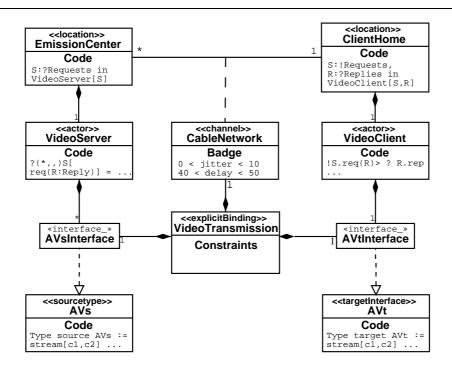

| 6.10 | A Video Transmission Example in $\mathcal{A}rtOC$ UML notation 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

14 LIST OF FIGURES

## Chapter 1

## Introduction

If one wishes to classify today's omnipresent computational devices he or she may not afford to miss, without ruining the relevance of his or her study, the class of artefacts that exhibit a time-constrained behavior. Examples rise in very dissimilar places and environments, to name a few: embedded systems such as electronic houseware (multiparted high-fidelity systems, television set-top boxes) or avionic sytems (telemetric devices, guiding devices), telecommunication systems (network switches, voice and video transportation using data-oriented communication protocols), control systems for nuclear plants and railroads, and finally computer games and graphic animation.

We are interested in real-time software engineering. Clearly, from the variety of systems that are mentioned above, one may guess that a tremendous number of very different proposals have been made in this domain to master program specification, design, development, testing and execution. To trace a rough outline however, software assurance still relies mainly on empirical, ad-hoc techniques for the first four steps, while execution correctness is ususally maintained by over-provisioning of resources. In a general fashion, the more an application is unpredictable, the less solutions exist to easily create it, and the more over-provisioning should be done. Yet, flexible real-time applications, which are inherently unpredictable, are now required to be created as witnessed by the recently issued Object Management Group (OMG) and Unified Modeling Language (UML) proposals.

To cope with these problems, we advocate the use of formal methods in each and every life-cycle step of flexible real-time applications; this should improve the confidence one may have in them. However, not being ambitious enough to propose a general method, we restrict our target: we consider only applications with hard real-time requirements, and we propose analysis methods for non-probabilitic models that only issue true/false answers (no probabilities, like e.g. "40% correct"). Furthermore, we take the "flexible applications" to be "open distributed applications" in the sense of the Open Distributed Processing Reference Model (RM-ODP) [ODP95], which have many implications that we now detail.

Distribution is indeed a major concern that we may not avoid, as illustrated by many of the industrial applications mentioned above. A distributed system is said to be open [ODP95] if it may be extended, updated or reconfigured at run-time. To have *extendable* systems stresses the need of creating inter-operable software mod-

16 Introduction

ules that are able to perform in inaccurately known environments while preserving their individual properties, hence allowing easy composition. In turn, to be able to update some components requires a notion of refinement (it is sometimes also called implementation, and its dual notion is abstraction) defining the conditions allowing some refined component to replace another one while preserving the supposedly correct behavior of the whole system. Finally, reconfigurability implies that the communication topology among given components may be modified, for example existing links may fall, or new ones may be established.

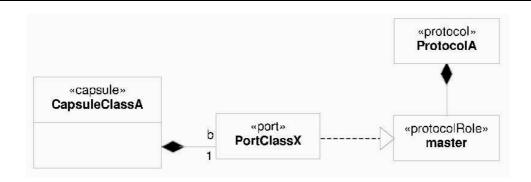

Object-Oriented Concurrent Programming (OOCP) provides the structuring concepts that we need. An object is a computational entity that encapsulates its own data and behavior. Each object may interact with the outside world through one or many interfaces. When interfaces are sufficiently well-defined, an object may be viewed as an independant software module and compositional techniques may be applied easily. Furthermore, interface subtyping and polymorphism allow refinement to be performed, while object references can be passed around among objects, simulating reconfiguration.

Numerous formal theories for compositionality and refinement have been devised during the last twenty years, many of them coping with concurrent objects either directly or through faithful encodings. A large body of work independently concerns real-time aspects of software. Surprisingly, though informal or applicative papers dealing with both aspects have been published, we know none but very few such proposals using formal methods.

We therefore propose to alleviate this lack by providing a timed process algebra derived from the  $\pi$ -calculus [MPW92]. We chose the  $\pi$ -calculus because it has a thoroughly developped and well-studied theory of expressiveness, equivalence, object encoding and implementability issues. We show how to deal with some of these issues in a timed setting: we give an appropriate notion of equivalence between objects, axiomatic proof rules to decide equivalence over finite terms, and a static analysis (type-theoretic) method to check that objects of some potentially infinite-state configuration are well-behaved regarding one another. This method naturally leads to view objects as bound by contracts, their interfaces stating which role they should play in each contract.

Direct applications are proposed for concurrent object-oriented modeling and QoS-enforcing middleware engineering. We show that our concepts are actually very similar to the ones introduced by the UML-RT [GBSS98, Sol97, RS] proposal. This is interesting since [RS] explicitly calls for object (i.e. contract) compatibility decision procedures. Our application to middleware is based on informal existent proposals [Sch00, MNCK99] for QoS-enforcing, real-time execution support. We propose to use our language for application coordination purposes [GC92], as done by the "model components" of [MNCK99]. Then, a program asking to be executed may either carry a proof of its correctness obtained by anterior verification (the proof can be checked by the platform [NL96]) or be type-checked on location as in the Java Virtual Machine (JVM) [Mic95].

We now give a more detailed, chapter by chapter, account of this thesis.

The first chapter after this introduction recalls the essential concepts defined in RM-ODP. This constitutes a convenient repository of concepts over which we shall

elaborate many of our later developements.

In Chapter 3 we introduce our calculus for timed processes with synchronous interactions, that we call  $\pi^{\delta}$ . We propose an operational semantics for it that yield labelled transition systems with which timed computations can be represented. The operators of our language are strictly more powerful than the operators present in all timed process algerba that we know of. This brings us to propose an original model for processes, allowing them to distinguish mandatory from possible actions. In case a component should fail to provide the required behavior, an explicit contract violation occurs, stopping the system. We obtain a calculus in which we are able to directly express contracts between components.

This should be seen as a natural introduction of deontic logic [MW93] concepts into process algebras. Previous works in the converse direction have been accomplished by Fiadeiro and Maibaum in an untimed temporal logic setting [FM91], and by Dignum and Kuiper in a timed temporal logic setting [DK97].

In Chapter 4 we propose a proof system deciding a form of late timed bisimulation equivalence for finite terms of our calculus. In order to do that, we must devise a symbolic (also called abstract) semantics for the terms of our calculus. This semantics is largely the result of a combination of two symbolic bisimulations [HL95] proposed for the  $\pi$ -calculus [Lin94] and for a calculus of timed automata [LY00]. In a nutshell, it combines two abstractions: an abtraction of clock values (which are uncountably-many), and an abstraction on port names of the  $\pi$ -calculus (which are infinitely-many, but countable). Having those abstractions allows us to give a finite interpretation over which our proof system is based. Due to the properties of our models, we however have to depart quite largely from the axiomations using symbolic bisimulations proposed in [Lin94] and [LY00].

In Chapter 5 we provide a behavioral type system for the language defined in Chapter 3. This type system allows, for a subset of potentially infinite-state configurations, to check that no error occurs due to a contract violation. The method is compositionnal by essence, using some kind of assume/guarantee reasoning: for an open system, a well-typing result states that no communication error may occur (guarantee) under the condition that any environment provided for it is well-typed as well (assumption). In that case, a type corresponds to a deterministic specification of the interface between a component and its environment. A notion of subtyping is also defined, allowing the  $substitution\ principle$  to be applied: any component of type A may be replaced by another component of type B provided that A is a subtype of B, noted  $A \leq B$ . We hence obtain a top-down way of building safe configurations by successive refinements.

In Chapter 6 we first present a short overview about the notion of contract, as it can be found in existing proof systems and specification laguages. We then propose two applications for our development technique. The first proposal promotes the use of  $\pi^{\delta}$  in real-time middleware, for monitoring, security, and evaluation purposes. The second second proposal is directed towards the less formal but more widespread UML-RT notation for real-time software engineering. We show the concepts defined in the theory for  $\pi^{\delta}$  can be used advantageously to encode UML-RT specifications. We then take an example of such conception using  $\pi^{\delta}$ .

The final chapter is devoted to our conclusions.

18 Introduction

## Chapter 2

## Open Distributed Processing and Real-Time

### 2.1 Open Distributed Processing

#### 2.1.1 Overview

The goal of the *Open Distributed Processing* standard [ODP95] has been, since its introduction in 1995, to provide a reference model precisely identifying which concepts and relations should be used during the development of distributed applications. In particular, RM-ODP promotes multi-aspect specification, object encapsulation, model composition/decomposition, and model abstraction/refinement. RM-ODP is conversely not tied to any concrete notation or modeling language, and it is the responsibility of the application designer to define or select languages for system description where RM-ODP concepts can be represented the most easily.

ODP introduces five viewpoints from which the development of a given application can be considered. Each viewpoint is suited for the expression of a particular aspect of the application. However, a given property may have several aspects, concerning many viewpoints: viewpoints may overlap (and they usually do). ODP hence fosters the use of formal method to help establishing viewpoint consistency. The following viewpoints definitions are given in the first part of the standard [ODP95].

- The *enterprise* viewpoint: a viewpoint on the system and its environment that focuses on the goals and policies retained for the system.

- The *information* viewpoint: a viewpoint on the system and its environment that focuses on information significance and information processing issues.

- The *computational* viewpoint: a viewpoint on the system and its environment that enables the expression of distribution-related issues by attaching functionalities of the system to distributed computational entities called *objects*.

- The *engineering* viewpoint: a viewpoint on the system and its environment that focuses on the mechanisms and functions required to support distributed interaction between objects in the system.

• The *technology* viewpoint: a viewpoint on the system and its environment that focuses on the choices of technologies for that system.

#### 2.1.2 The Computational Viewpoint

Our interests will focus on the computational viewpoint. In that viewpoint, the application is modeled as an evolving set of objects having interfaces that they use to interact synchronously or asynchronously with other objects over supposedly perfect or lossy channels.

#### 2.1.2.1 Objects and Services

Objects are constituted of an arbitrary behavior and a finite encapsulated data set. Concrete computational modeling languages have to respect two principles in order to be ODP-compliant. The *object abstraction* principle says the programmer may ignore irrelevant details: an object may be the result of the composition of other objects, an object may have any granularity (e.g. from a simple integer to a complex factory system), and the services offered by an object may be described in a way independent of its implementation. The  $data\ encapsulation$  principle oppositely restrains object behavior: the only way an object B has to produce a side effect on the data of an object A is by calling a method of A.

An object may provide or access services through its *interfaces*. An interface is a set of available methods together with conditions indicating when each method may be invoked. An interface will be said to play a *role* in the provision of some service. Two examples of roles are the *server* that provides a service, and the *client* that accesses it. Services (and interfaces) come in two flavors: flow services and operational services.

ODP indeed distinguishes two forms of object interactions. Flow services are intended to abstractly represent continous interactions: the source role of a flow service sends a stream of data to the target role of that service. Operational services oppositely discern each interaction as an individual event: an operation call occurs between a client and a server role, resulting in a method invocation on the object owning the server role. An operation can be either an interrogation, where the server returns a response, or an announcement, where no response is sent to the client. An example configuration of objects communicating through operational interfaces is presented on Figure 2.1.

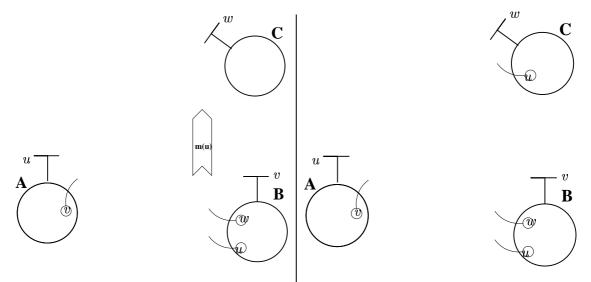

The object on the left possesses an interface holding the client role of a service u. Its invocations always concerns the server interface for u that is owned by the object on the right. Signals for operation invocation are conveyed by messages, and on our example a message carrying signal m circulates from the client to the server. If m is an interrogation operation, then a reply signal also named m will be sent later by the server. It can be seen that roles and interfaces may confound easily, and we will not restrict from making this confusion, often using "role r" for "interface playing role r"; should the meaning not be clear from context, we shall always give necessary precisions.

Figure 2.1: Communicating roles of an Operational Service u

#### 2.1.2.2 Passing Roles Around

We now show how a given configuration may dynamically evolve by passing around the roles it possesses. A message may indeed be sent with roles as effective parameters, as channels can be passed around in formalisms such as the  $\pi$ -calculus. An example illustrating this feature is depicted in Figures 2.2 and 2.3.

Figure 2.2: An example of communicating interfaces, step (1)

Figure 2.3: An example of communicating interfaces, step (2)

The message m shown on Figure 2.2 has been sent by object **B**. It features a copy of the client role of service u as effective parameter, and it is received by object **C** on Figure 2.3. The object **C** now has the capability to send messages to the owner **A** of the server role of service u. As so does object **B** (it did not loose its client role on u but sent a copy of it), both **B** and **C** can concurrently access service u provided by object **A**.

#### 2.1.2.3 Contracts and Object Binding

When reasoning about services and object interactions, a fundamental point is the possibility to explicitly declare, negociate, observe and enforce applicative Quality of Service (QoS) properties. RM-ODP tackles this issue by introducing the pervasive

notion of contract among entities. A contract is a written document enclosing the nun-functionnal properties sustained by a service provider or required by a service accessor. The establishment of a service session is generally called binding. In a binding the accessor and provider objects are bound under the rules of some contract. A contract may itself include rules declaring how object binding must be done in order to properly establish the corresponding service. RM-ODP then separates two cases. If the contract imposes that any object willing to become client of a service must (directly or indirectly) contact the provider before establishing the service, then the binding procedure is said explicit. A binding object may then be created upon service establishment to manage the connection: if the contract is broken by some faulty object involved in it, the binding object may either shut the service or take any necessary measure in conformance with the contract terms. On the other side if any object can access a service without pledging allegiance to the server beforehand the binding is said implicit and no binding object may be created.

It is often that the writing of contracts actually becomes unnecessary when some contract framework is used. A contract framework contains service-kind specific molds for contracts: when applied to a service of some kind, a mold produces the contract ruling that service. A contract mold describes how the service must be established (i.e. binding rules) and under which conditions the contract can be maintained. The latter rules imply a definition of role compatibility (i.e. peered roles are well-behaved regarding each other), a notion that leads to contract consistency (i.e. a contract is consistent iff its roles are compatible). Under a contract framework, the notions of service and contract may therefore be united without further concern.

In conclusion we underline that having formally-defined contracts may clearly allow for both modular specifications (they can be compared to the abstract data types of sequential programming) and compositionnal verification.

#### 2.1.3 The Engineering Viewpoint

We will refer to the engineering viewpoint in the application part of this thesis. Yet we now provide a short overview of it.

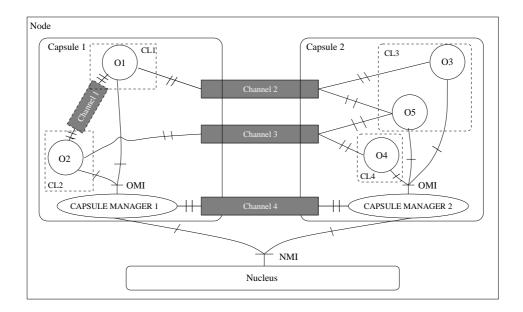

At engineering level, objects are not distribution-aware anymore. Instead, they are considered according to the architecture which Figure 2.1.3 is an example. A node is the physical unit for distribution. It contains capsules, which are the unit for processing and failure (eg UNIX processes). Within capsules, highly-interacting objects are then grouped into clusters. Each node has a nucleus, that provides a service to the capsules of its node through an interface called the Node Management Interface (NMI). Each capsule has a capsule manager object that provides a service to the objects of its capsule through the interface similarly called the Object Management Interface (OMI). The nucleus can be seen as the operating system kernel of the node, whereas capsule managers can be seen as virtual machines executing clusters of objects.

Objects within a cluster are linked directly by their interfaces, whereas other objects must use *channels*. Channels encompass stub objects (for marshalling, etc.), binder objects (to administrate the link), and protocol objects (for communications).

Figure 2.4: An ODP Configuration at Engineering Level

#### 2.1.4 Specifications, Viewpoints and their Relations

As suggested by [BS97], engineering and computational viewpoint specifications should use the same language. Following this proposition, we use ArtOC along those different activities. Hence, the Virtual Machine (VM) specification is given at engineering level by the system architect, while user objects are viewed at computational level by the application designer. Each objet from a given user application is subsequently mapped to one at engineering level.

It should however remain to the mind of the reader that the semantics of  $\mathcal{A}$ rtOC is essentially different at those two levels: a computational view implies maximum parallelism, whereas engineering view implies concurrency through interleaving within each capsule. The goal of the VM architecture and policies is to preserve the computational level semantics at engineering level: they can be considered equivalent if any required resource at computational level is granted at engineering level.